***THIS DOCUMENT IS FOR MAINTENANCE

PURPOSES ONLY AND IS NOT

RECOMMENDED FOR NEW DESIGNS***

# SP8716/8/9

## 520MHz LOW CURRENT TWO-MODULUS DIVIDERS

SP8716 ÷ 40/41, SP8718 ÷ 64/65, SP8719 ÷ 80/81 are 50mW programmable dividers with a maximum specified operating frequency of 520MHz over the temperature range -40 °C to + 85 °C.

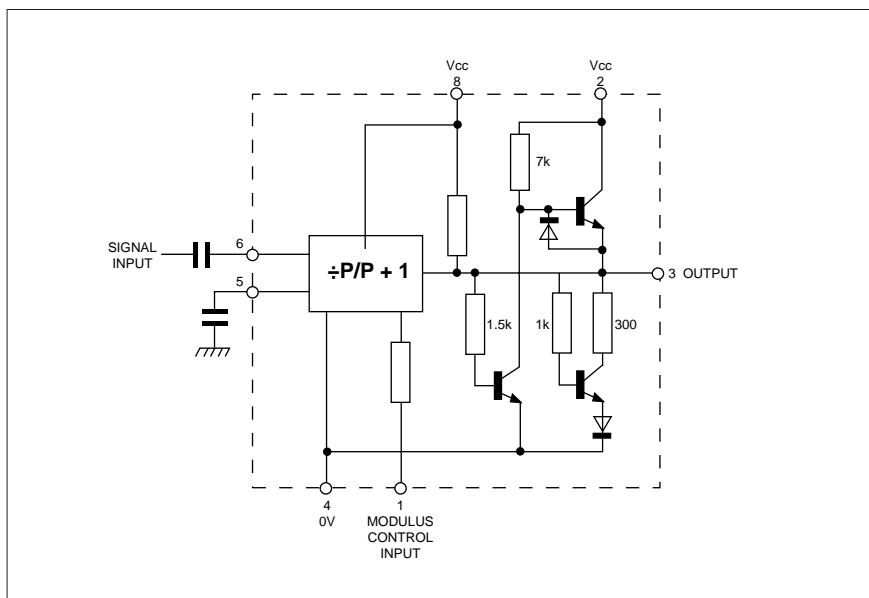

The signal (clock) inputs are biased internally and require to be capacitor coupled. The output stage is of an unusual low power design featuring dynamic pull-up, and optimised for driving CMOS. The 0 to 1 output edge should be used to give the best loop delay performance.

## FEATURES

- DC to 520MHz Operation

- -40°C to +85°C Temperature Range

- Control Inputs and Outputs are CMOS Compatible

## QUICK REFERENCE DATA

■ Supply Voltage 5.0V ± 0.25V

■ Supply Current 10.5mA typ.

## ABSOLUTE MAXIMUM RATINGS

|                             |                 |

|-----------------------------|-----------------|

| Supply voltage pin 2 or 8): | 8V              |

| Storage temperature range:  | -55°C to +150°C |

| Max. Junction temperature:  | +175°C          |

| Max. clock I/P voltage:     | 2.5V p-p        |

Figure 2 : Functional diagram

## ELECTRICAL CHARACTERISTICS

## Test conditions (unless otherwise stated):

Supply voltage:  $V_{CC} = +4.95$  to  $5.45$  V, Temperature:  $T_{amb} = -40$ °C to  $+85$ °C

| Characteristics                 | Symbol    | Value            |      | Units | Conditions                    | Notes |

|---------------------------------|-----------|------------------|------|-------|-------------------------------|-------|

|                                 |           | Min.             | Max. |       |                               |       |

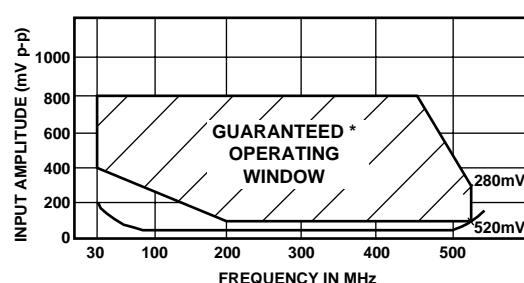

| Max. frequency                  | $f_{max}$ | 520              |      | MHz   | Input 100-280mV p-p           | 1     |

| Min. frequency (sinewave input) | $f_{min}$ |                  | 30   | MHz   | Input 400-800mV p-p           | 2     |

| Power supply current            | $I_{CC}$  |                  | 11.9 | mA    | $CL = 3pF$ ; pins 2, 8 linked | 1     |

| Output high voltage             | $V_{OH}$  | $(V_{CC} - 1.2)$ |      | V     | $IL = -0.2mA$                 | 1     |

| Output low voltage              | $V_{OL}$  |                  | 1    | V     | $IL = 0.2mA$                  | 1     |

| Control input high voltage      | $V_{INH}$ | 3.3              | 8    | V     | $\div P$                      | 1     |

| Control input low voltage       | $V_{INL}$ | 0                | 1.7  | V     | $\div P + 1$                  | 1     |

| Control input high current      | $V_{INH}$ |                  | 0.41 | mA    | $V_{INH} = 8V$                | 1     |

| Control input low current       | $V_{INL}$ | -0.20            |      | mA    | $V_{INL} = 0V$                | 1     |

| Clock to output delay           | $t_p$     |                  | 28   | ns    | $CL = 10pF$                   | 2     |

| Set-up time                     | $t_s$     | 10               |      | ns    | $CL = 10pF$                   | 2     |

| Release time                    | $t_r$     | 10               |      | ns    | $CL = 10pF$                   | 2     |

## NOTES

- Tested at 25°C only

- Guaranteed but not tested

## NOTE

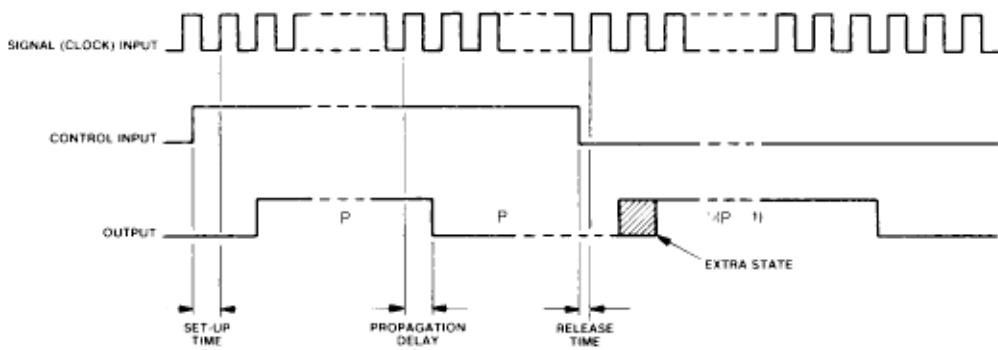

The set-up time  $t_s$  is defined as the minimum time that can elapse between a L  $\rightarrow$  H transition of the control input and the next L  $\rightarrow$  H clock pulse transition to ensure that the  $\div P$  mode is obtained.

The release time  $t_r$  is defined as the minimum time that can elapse between a H  $\rightarrow$  L transition of the control input and the next L  $\rightarrow$  H clock pulse transition to ensure that the  $\div(P + 1)$  mode is obtained.

Figure 3 : Timing diagram

\*Tested as specified in table of Electrical Characteristics

Figure 4 : Typical input characteristics

## OPERATING NOTES

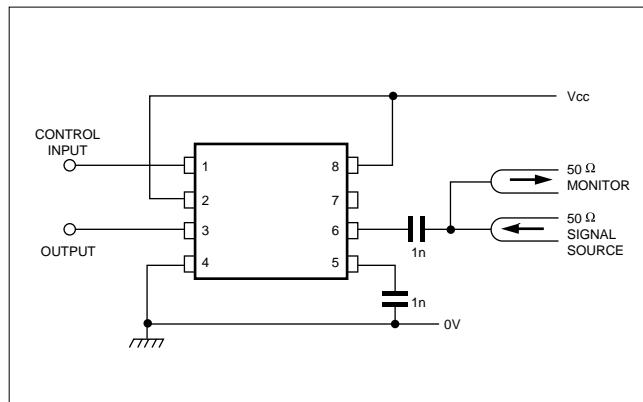

1. The inputs are biased internally and coupled to a signal source with suitable capacitors.

2. If no signal is present the devices will self-oscillate. If this is undesirable it may be prevented by connecting a 15k resistor from one input to pin 4 (ground). This will reduce the sensitivity.

3. The circuits will operate down to DC but slew rate must be better than 100V//us.

4. The output stage is of an unusual design and is intended to interface with CMOS. External pull-up resistors or circuits must not be used.

5. This device is NOT suitable for driving TTL or its derivatives.

Figure 5: Toggle frequency test circuit

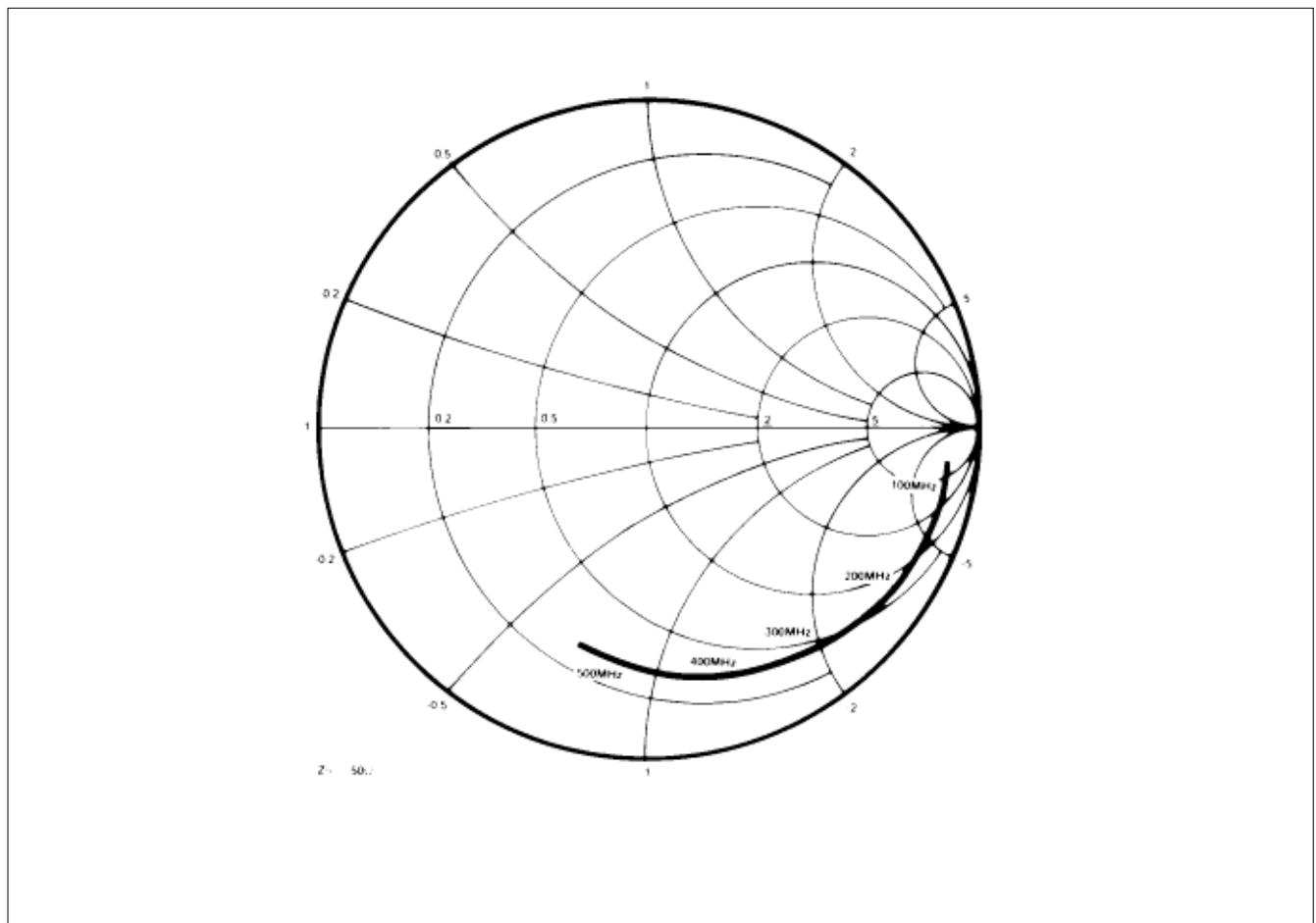

Figure 6 : Typical input impedance

<http://www.zarlink.com>

**World Headquarters - Canada**

Tel: +1 (613) 592 0200

Fax: +1 (613) 592 1010

**North America - West Coast**

Tel: (858) 675-3400

Fax: (858) 675-3450

**North America - East Coast**

Tel: (978) 322-4800

Fax: (978) 322-4888

**Asia/Pacific**

Tel: +65 333 6193

Fax: +65 333 6192

**Europe, Middle East,

and Africa (EMEA)**

Tel: +44 (0) 1793 518528

Fax: +44 (0) 1793 518581

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink Semiconductor's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in an I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2001, Zarlink Semiconductor Inc. All rights reserved.